友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

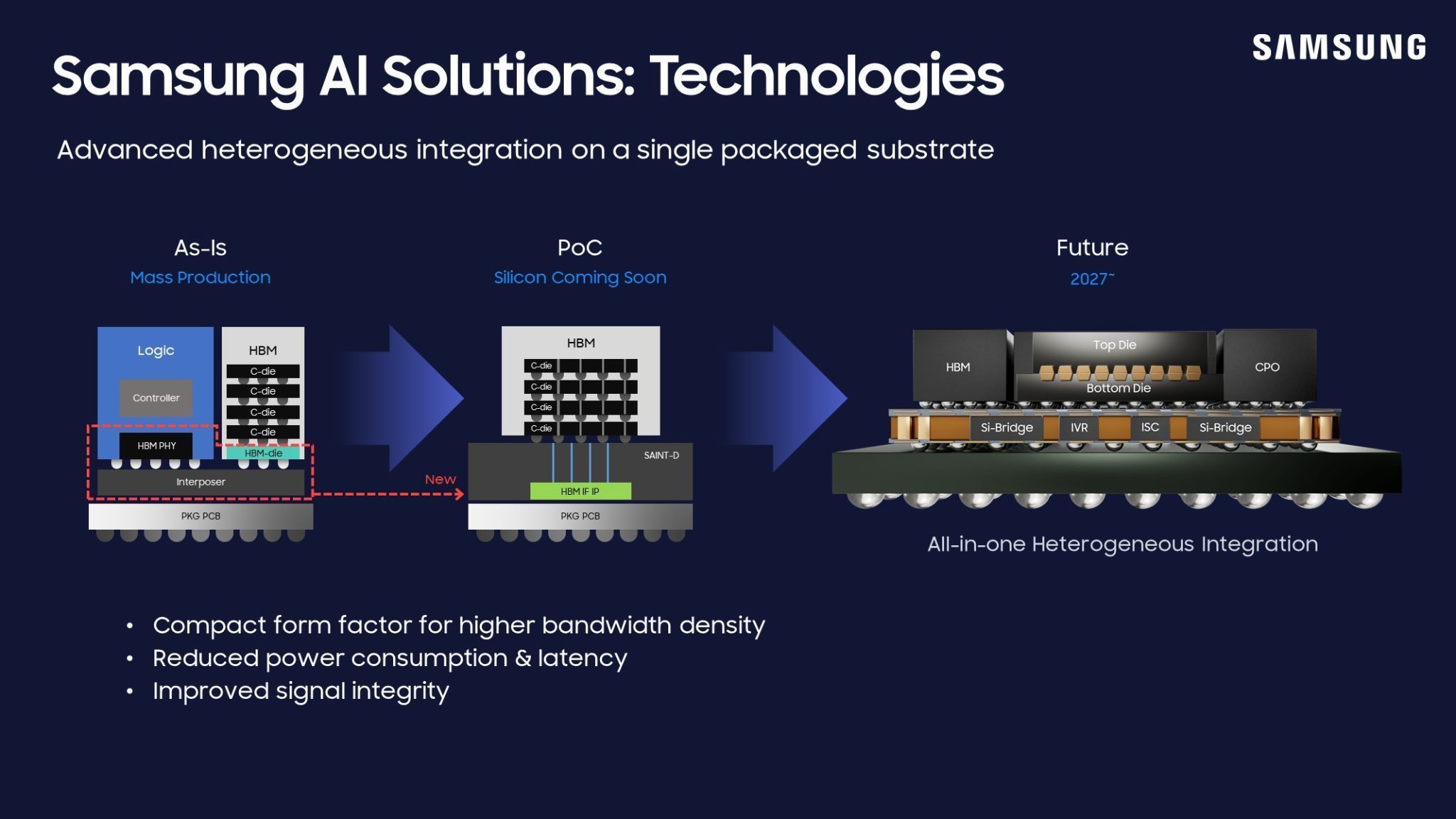

三星年内有望推出 3D HBM 封装技术 SAINT-D,或改变 AI 芯片规则

20

0

相关文章

近七日浏览最多

最新文章

标签云

三星

苹果

超广角

长焦镜头

iphone

京东方

显示屏

oled

苹果公司

系列芯片

韩国

美国

核电

知名企业

企事业单位

deepseek

豆瓣

顶流

探案

大奉打更人

华为

互联网

小手机

手机厂商

市场份额

折叠产品线

大陆

台积电

英伟达

中芯国际

芯片代工

芯片制造商

台湾积体电路制造

安卓

苹果手机

华为手机

智能手机

黄仁勋

英特尔

amd

芯片供应

折叠

手机

黑科技

余承东

屏幕铰链

新品发布会

俄罗斯

应用商店

财务会计

财务报表

安卓手机

芯片

路透社

三星电子

ui

android

美光

sk

cmos

pi

吉利

redmi

lcd

4g

国产品牌

现代汽车

世界500强

dram

pdd

操作系统

小米

soc

gpu

xperia

索尼

高通

联发科

arm

处理器

自研芯片

小米集团

说句实话

骁龙至尊版

白手套

芯片领域

酷睿

硬盘

主机

内存

性价比

mini

电池容量

骁龙

华为公司

se

微星

vivo

小米公司

防水

apple

iqoo

npu

cpu

天风证券

归母净利润

英特尔酷睿

更上一层楼

ultra

酷睿处理器

游戏

显卡

千元机

联发科天玑

ois

reno

毛利率

荣耀10

写真

小米mix

红米手机

usb30

独立显卡

绝地求生

文旅

河北

黄青

中国移动

宏碁

pilot

巫师3

switch

v10

原神

nfc

红魔

快科技

q4

intel

ddr5

安兔兔

何小鹏

华为云

云空间

摄影

choi

linux

笔记本电脑

金立

捐款

雅安市

雅安地震

逮捕

中国

间谍罪

反间谍法

韩国公民

莫迪

印度警方

三星罢工抗议

大屏幕

手机市场

手机行业

卷曲屏手机

华为mate

交易所

韩国央行

人工智能

半导体

共享单车

雷军

sk海力士

股价

asml

光刻机

特斯拉

商业内幕

微软

抗议活动

娃哈哈

宗馥莉

小鹏汽车

抖音

清华大学

人均gdp

股票

林剑

外交部

美国政府

经贸问题

机器人技术

nvidia

商务部

eda

半导体公司

半导体领域

网络攻击

中国政府

荷兰防相

卢伟冰

澎湃

小米造芯

影驰

rtx

系列显卡

海关

关税

税号

首席执行官

美国商务部

药品

仿制药

白宫

美媒

科技巨头

海湖庄园晚宴

唐纳德特朗普

荷兰

碳化硅

德国

nsa

grok

埃隆_马斯克

豪威

微电子

民营企业家

欧洲

英伟达gpu

国际消费电子展

OpenAI

疯狂

贝尼奥夫

钛媒体

a100

大语言模型

算法

老子

代码

非公版

字节跳动

blackwell

内存条

颗粒ddr5

垄断

谷歌

烟草

张泉灵

周一

拜登政府

出口限制

乔拜登

互联网协会

国家安全

多核

高通骁龙

全大核架构

mate70