友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

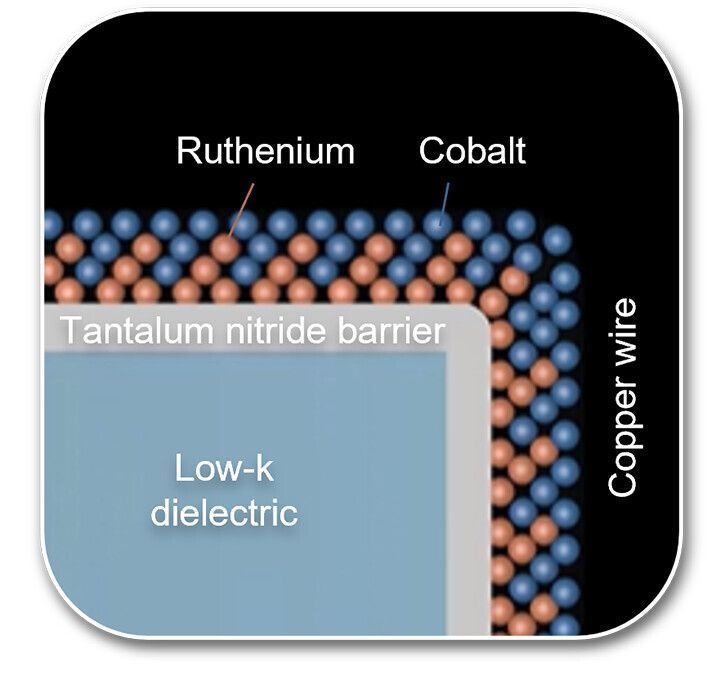

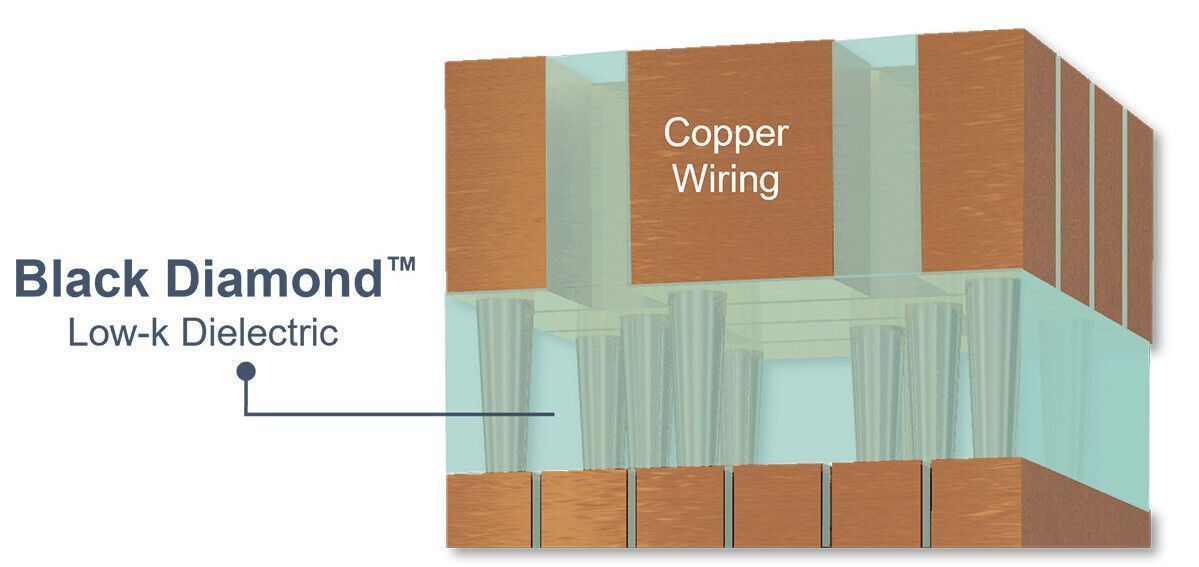

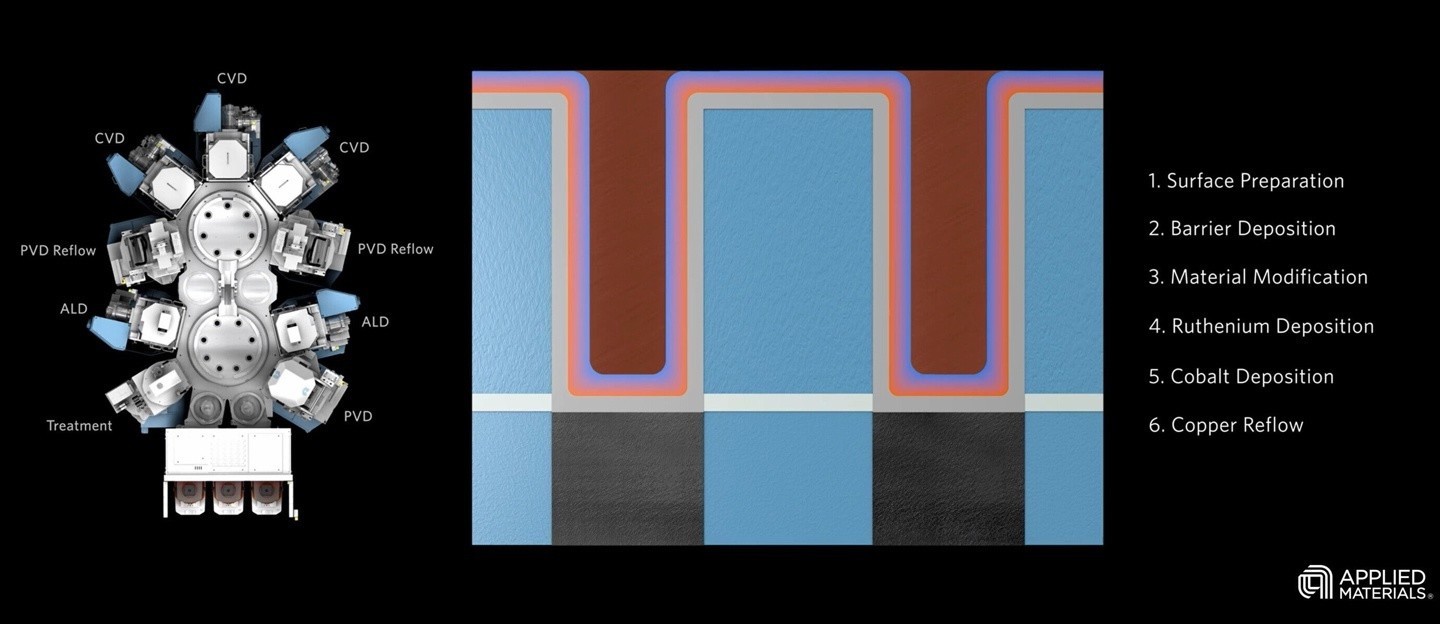

应用材料创新芯片布线工艺:量产中首次使用钌,电阻最高降幅 25%

1

0

相关文章

近七日浏览最多

最新文章

标签云

芯片

批量

黄仁勋

科技巨头

英伟达ceo

blackwell

间谍

情报机关

国家安全部

eco

基准利率

mac

韩国央行

韩国

微软

美股

亚马逊

美国

英特尔

英伟达

cpu

三星

路透社

三星电子

美光

sk

贵州茅台

京东物流

茅台集团

茅台酒

投资

茅台

工业机器人

lucid

优步

新东方

半导体

马斯克

初创公司

戴尔

人工智能

jonathan

john

谷歌

gpu

a股

日元

日本央行

无人机

中国

毛利率

摩根士丹利

快科技

国际

科技

半导体产业

光刻机

原子弹

neura

外部世界

美国司法部

apple

股价

科学家

自动驾驶

特斯拉

擎天柱

第一财经

超级工厂

智能驾驶